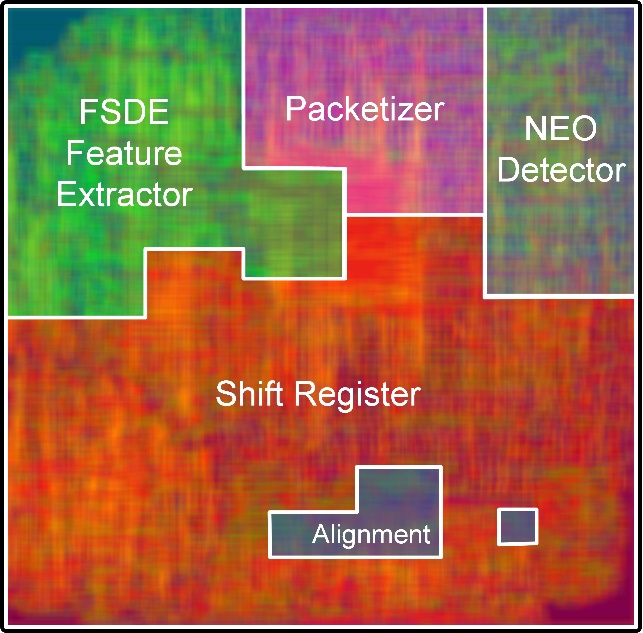

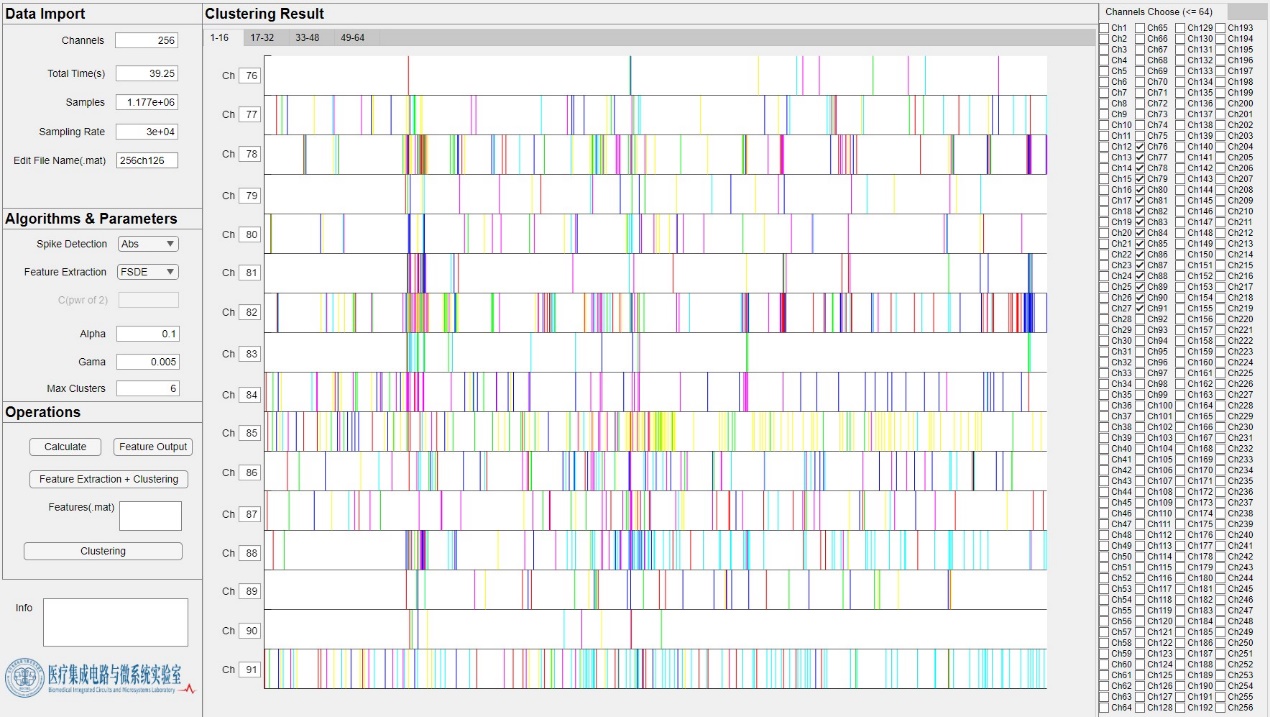

下一代无线脑机接口(BCI)设备需要专用的神经信号处理器(NSP)从而在给定的功耗和传输带宽限制下提取关键的神经信息。在神经学研究和临床应用中,尖峰检测和聚类是重要的信号处理步骤。本工作基于对硬件计算友好的尖峰检测和特征提取算法的系统评估,提出非线性能量算子(NEO)、一阶和二阶导数(FSDE)与“扰动”K均值聚类等算法,共同实现最优的准确性性能。NSP ASIC采用通道交织架构使功耗和面积最小化,在65纳米CMOS工艺技术下NSP每通道功率消耗2微瓦,面积占用0.0057平方毫米。所提出系统实现了92%的无监督尖峰分类准确率和98.3%的数据速率降低,显示了应用在高通道数无线BCI的巨大潜力。

Next generation of brain-computer interface (BCI) aspires to achieve accurate and real-time spike sorting while being power--efficient. To achieve on-chip high-channel-count neural signal processing, accurate and hardware-efficient algorithms are critical. This work proposes a spike-sorting system that includes a NEO spike detector with an automatic threshold trainer, spike alignment and a feature extractor based on the first-and-second-derivative (FSDE) algorithm. The system employs a time-interleaving structure to reuse the logic cells, thus reducing the area and leakage power. The proposed system is implemented in ASIC in both 65 nm and 180 nm CMOS technologies with different folding ratios, and the product of power and area is optimized when a DSP core interleaves 8 channels. The implemented design in a 65-nm technology occupies 2.69 x 10-3 mm2/channel and consumes 0.52 mW/channel at a 1.2-V supply. The accuracy simulations show that the proposed NEO (d = 1) and FSDE algorithms achieve the average spike-detection accuracy of 97.1% and clustering accuracy of 91.6%, respectively.